# Comparison of Conventional & New Multilevel Inverter Topology

Anjali Sudarsanan, Roopa R, Sanjana S

\_\_\_\_\_

**Abstract** — This paper deals with the comparison of conventional inverters to new multilevel inverter topologies. Their performance is highly superior to that of conventional two-level inverters due to reduced harmonic distortion, lower electromagnetic interference, and higher dc link voltages. By using conventional method the performance of the inverter is low. In this paper a new topology with reversing voltage component is suggested to improve the performance of multilevel inverter. This topology requires fewer components and therefore the cost and complexity is low.

Index Terms— Conventional Inverter, Multilevel Inverter, SPWM, Topology

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

# **1** INTRODUCTION

${f M}$ ultilevel power conversion was first introduced in the 19th century itself. The general concept involves utilizing minimum number of switches with minimum amount of supply a higher number of active semiconductor switches to perform the power conversion in small voltage steps. The smaller voltage steps lead to the production of higher power quality waveforms and also reduce voltage (dv/dt) stress on the load and the electromagnetic compatibility concerns [1]. Some new approaches have been recently suggested such as the topology utilizing low-switching-frequency high-power devices [2]. Although the topology has some modification to reduce output voltage distortion, the general disadvantage of t his method is that it has significant low-order current harmonics. It is also unable to exactly manipulate the magnitude of output voltage due to an adopted pulse width modulation (PWMmethod [3].

The section II deals with the comparison of conventional inverter and multilevel topology [4]-[5].Detailed study of implementation of new multilevel inverter topology is performed in section III [7]. Sections IV contain modulation techniques of conventional inverter topology and new multilevel inverter topology [6]. Section V, Experimental result of two inverters is performed.

- Anjali Sudarsanan is currently pursueing B.Tech degree in Electrical and Electronics, Kottayam Institutes of Technology and Science, india, anjalisudarsanan2@gmail.com

- Roopa R is currently pursueing B.Tech degree in Electrical and Electronics, Kottayam Institutes of Technology and Science, India,rooparamakrishnan001 @gmail.com

Sanjana S is currently pursueing B.Tech degree in Electrical and Electronics, Kottayam Institutes of Technology and Science, India,sanjanashenoy88 @gmail.com

# 2. COMPARISON OF CONVENTIONAL INVERTER AND NEW MULTILEVEL TOPOLOGY

#### **2.1. CONVENTIONAL INVERTER**

In conventional inverters mainly two level inverters are used to obtain a controllable voltage. The two level inverter is a circuit which consists of sources with some amount of voltage and many switches for controlling voltage or current. In high power and high voltage applications the conventional two level inverters, however, have some limitations in operating at high frequency mainly due to switching losses and constraints of the power device ratings. Series and parallel combination of power switches in order to achieve the power handling voltages and currents. Due to the presence of many switches and sources power loss is very high. In the conventional two level inverters the input DC is converted into the AC supply of desired frequency and voltage with the aid of semiconductor power switches. Depending on the configuration, four or six switches are used. A group of switches provide the positive half cycle at the output which is called as positive group switches and the other group which supplies the negative half cycle is called negative group.

Some new approaches have been recently suggested such as the topology utilizing low-switching-frequency high-power devices ,complex circuits can often seen in two level inverter circuits, due to its complexity and cost also increases.

#### 2.2 .MULTILEVEL INVERTER TOPOLOGY

#### 2.2.1 Diode-Clamped Inverter

In diode clamped inverter we use diodes for rectifi-

cation as well as for controlling the sources and output. By using this method harmonics as well as using of switching can be reduced. This will produce ripples which is comparatively less than two level inverter thus obtaining a better output. For example in Fig.1 a five-level diode-clamped inverter is shown in which the dc bus consists of four capacitors, and diodes are used. For dc-bus voltage Vdc, the voltage across each capacitor is Vdc/4, and each device voltage stress will be limited to one capacitor voltage level Vdc/4 through clamping diodes. Here by the action of diodes and capacitors voltage can be controlled.

Fig.1. Five-level Diode-clamped multilevel inverter circuit topology.

#### 2.2.2 Capacitor-Clamped Inverter

In capacitor clamped inverters we use flying capacitor to control the voltage. We know that capacitor has the property of charging and discharging this property help the inverter for controlling the source as well as output. For example in Fig. 2 illustrates the fundamental building block of a phase-leg capacitor-clamped inverter. The circuit has been called the flying capacitor inverter. The voltage synthesis in a five-level capacitor-clamped converter has more flexibility than a diodeclamped.

Fig.2.Five-level Capacitor-clamped multilevel inverter circuit

A different converter topology is introduced here, which is based on the series connection of singlephase inverters with separate dc sources. For example in Fig.3 shows the power circuit for one phase leg of a five-level inverter with one cell in each phase. The resulting phase voltage is synthesized by the addition of the voltages generated by this cell.

Figure 3: one phase leg of a five-level inverter with one Hbridge cell.

#### 3. NEW MULTILEVEL TOPOLOGY

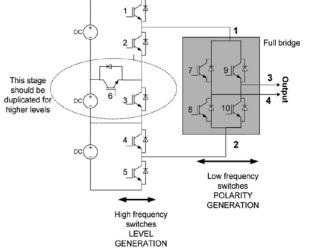

In this paper we are using new hybrid topologies which have several advantages over conventional inverters. In conventional multilevel inverters, many semiconductor switches are combined to produce a high-frequency waveform. In this paper this idea of conventional is also considered to produce new topology. This topology consists of two parts mainly level generation part and polarity generation part. The topology combines the two parts (high frequency and low frequency) to generate the multilevel voltage output. In order to generate a complete multilevel output, the positive levels are generated by level generation part. And then, this part is fed to a polarity generation which will generate the required polarity for the output. This will eliminate many of the semiconductor switches which were responsible to generate the output voltage levels in positive and negative polarities.

The RV topology in seven levels is shown in Fig. 4. As can be seen, it requires minimum number of switches and three isolated sources. The principal idea of this topology as a multilevel inverter is that by using the level generator left stage in Fig. 4 we can switch the switches according to our need and produce desired positive output and switches are offed to obtain complete positive part .For negative part we use polarity generator the right circuit in fig 4 which provide negative part by switching action.

#### 2.2.3 Cascaded Multicell (H-Bridge) Inverters.

Fig.4. Schematic of a seven-level inverter in single phase.

It decides about the polarity of the output voltage. This part, which is named polarity generation, transfers the required output level to the output with the same direction or opposite direction according to the required output polarity. It reverses the voltage direction when the voltage polarity requires to be changed for negative polarity.

It can also be applied for three-phase applications with the same principle. This topology uses isolated dc supplies. Therefore, it does not face voltage-balancing problems due to fixed dc voltage values. In comparison with a cascade topology, it requires just one-third of isolated power supplies used in a cascade-type inverter.

#### 4. MODULATION TECHNIQUES

#### 4.1 Conventional Inverter Topology

Ordinary PWM modulation for two-level inverters is accomplished through comparison between a reference wave and a triangular carrier. The reference wave have the frequency and amplitude wanted for the output voltage signal and the triangular carrier wave has the amplitude of half the DC input voltage, in an simple ordinary case, and

Its frequency is dependent on application but must be higher than the reference wave frequency [8].

#### 4.2 Multilevel Inverter Topology

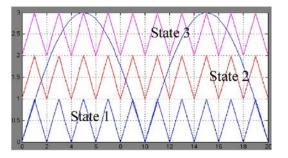

In this paper, PD SPWM is adopted for its simplicity. Here sinusoidal wave is taken as reference wave and triangular wave is taken as Carrier wave. They are also in phase with each other. The modulator and three carriers' stages for SPWM are shown in Fig. 5 [10].

Fig. 5. SPWM carrier and modulator for RV topology.

Multilevel PWM methods uses high switching frequency carrier waves in comparison to the reference waves to generate a sinusoidal output wave, much like in the two-level PWM case. To reduce harmonic distortions in the output signal phase-shifting techniques are used.

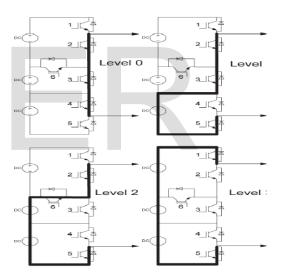

Fig. 6. Switching sequences for different level generation

According to the four mentioned suggestions, the sequences of switches (2–3-4), (2-3-5), (2-6-5), and (1, 5) are chosen for levels 0 up to 3, respectively. These sequences are shown in Fig. 6. As observed from Fig. 6, the output voltage levels are generated in this part by appropriate switching sequences. The ultimate output voltage level is the sum of voltage sources, which are included in the current path that is marked in bold.

| States  | O     | ne    | Two       |           | Th  | ree       |

|---------|-------|-------|-----------|-----------|-----|-----------|

| Compare | +     | -     | +         | -         | +   | -         |

| Mode    | 2-3-5 | 2-3-4 | 2-5-<br>6 | 2-3-<br>5 | 1-5 | 2-5-<br>6 |

Table I. Switching cases in each state according to Related comparator output

# 5. EXPERIMENTAL RESULT

| Si.No | Parameters            | Two level           | Multilevel |  |

|-------|-----------------------|---------------------|------------|--|

| 1     | Efficiency            | Low                 | High       |  |

| 2     | Harmonics             | High                | Low        |  |

| 3     | Output<br>Voltage     | Low                 | High       |  |

| 4     | Levels                | 3                   | >3         |  |

| 5     | Voltage<br>Regulation | Not Adjusta-<br>ble | Adjustable |  |

# 6. CONCLUSION

A comparative study of conventional inverter and a multilevel inverter is done in this paper. In each sections we discussed brief ideas and techniques used in the two level inverter, diode clamped, cascade, capacitor clamped inverters with new multilevel topology. This paper indicates that new multilevel topology have more advantages than the other methods. By using new multilevel topology harmonics can be reduced.

# 7. ACKNOWLEDGEMENT

Our sinciere thanks to Mrs Sijitta Issac (HOD, EEE department Kottayam Institute of Technology and Science) and also to Ms Amrutha Rose Thomas (Asst .Proffesor Kottayam Institute of Technology and Science) who supported us for completing our journel.

### 7. REFFERENCE

1] K. Jang-Hwan, S.-K. Sul, and P. N. Enjeti, "A carrier-based PWM method with optimal switching sequence for a multilevel four-leg voltage source inverter," *IEEE Trans. Ind. Appl.*, vol. 44, no. 4, pp. 1239–1248, Jul./Aug. 2008.

[2] G. M. Martins, J. A. Pomilio, S. Buso, and G. Spiazzi, "Three-phase lowfrequency commutation inverter for renewable energy systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1522–1528, Oct. 2006.

[3] S. Daher, J. Schmid, and F. L. M. Antunes, "Multilevel inverter topologies for stand-alone PV systems," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2703–2712, Jul. 2008.

[4] J. S. Lai and F. Z. Peng, "Multilevel converters–A new breed of power converters," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 509–517, May/June 1996.

[5] R. Teodorescu, F. Beaabjerg, J. K. Pedersen, E. Cengelci, S. Sulistijo, B. Woo, and P. Enjeti, "Multilevel converters – A survey," in *Proc. European Power Electronics Conf. (EPE'99)*, Lausanne, Switzerland, 1999, CD-ROM.

[6] A. Radan, A. H. Shahirinia, and M. Falahi, "Evaluation of carrier-based PWM methods for multi-level inverters," in *Proc. IEEE ISIE*, 2007, pp. 389–394.

[7] G. Mondal, K. Gopakumar, P. N. Tekwani, and E. Levi, "A reducedswitch- count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2344–2351, Aug. 2007.

[8] Rodriguez, J.; Jih-Sheng Lai; Fang Zheng Peng; , "Multilevel inverters: a survey of topologies, controls, and applications," Industrial Electronics, IEEE Transactions on,vol.49, no.4, pp. 724-738, Aug 2002 doi: 10.1109/TIE.2002.801052.

[9] C. Hochgraf, R. Lasseter, D. Divan, and T. A. Lipo, "Comparison of multilevel inverters for static var compensation," in Conf. Rec. IEEE-IAS Annu. Meeting, Oct. 1994, pp. 921–928.

[10] McGrath, B.P.; Holmes, D.G.; , "A comparison of multicarrier PWM strategies for cascaded and neutral point clamped multilevel inverters," Power Electronics Specialists Conference, 2000. PESC 00. 2000 IEEE 31st Annual , vol.2, no., pp.674-679 vol.2, 2000 doi: 10.1109/PESC.2000.879898. International Journal of Scientific & Engineering Research, Volume 6, Issue 2, February-2015 ISSN 2229-5518

[11] Zhiguo Pan, Fang Zheng Peng, Keith A. Corzine, Victor R. Stefanovic, John M. (Mickey) Leuthen, and Slobodan Gataric, "Voltage Balancing Control of Diode-Clamped Multilevel Rectifier/Inverter Systems" IEEE Trans On Industry Applications, Vol. 41, No. 6, pp. 1698-1706, Nov/Dec 2005.

# IJSER